# M66335FP

## Facsimile Image Data Processor

REJ03F0276-0200 Rev.2.00 Jun 16, 2008

### **Description**

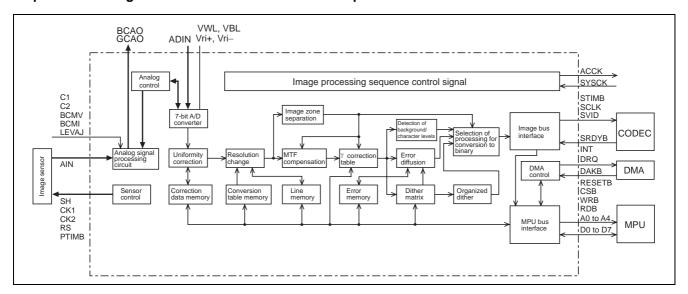

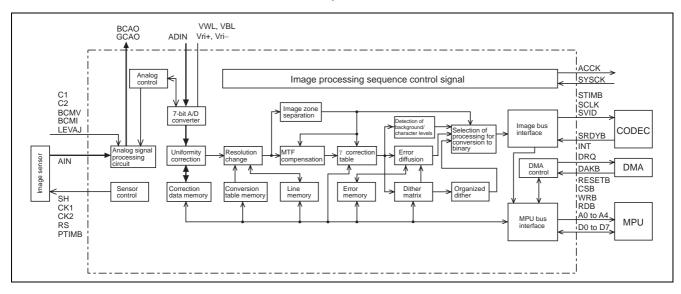

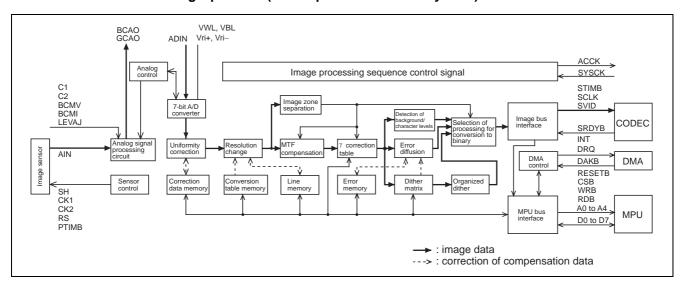

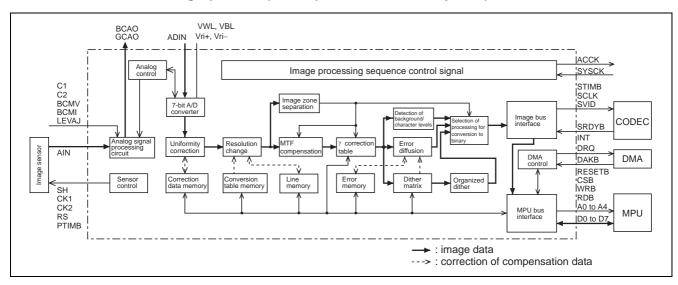

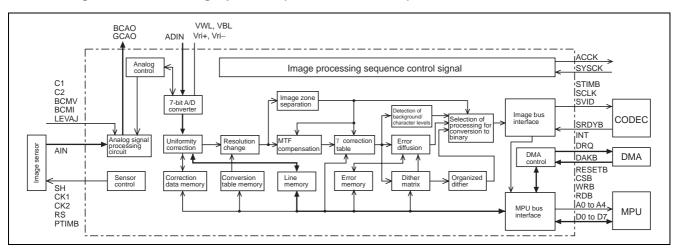

The M66335 is a facsimile image processing controller to turn into binary signals analog signals which have been output through photo-electric conversion by the image sensor.

The image processing functions includes peak value detection, uniformity correction, resolution change, MTF compensation,  $\gamma$  correction, detection of background/character levels, error diffusion, separation of image zones, and designation of regions.

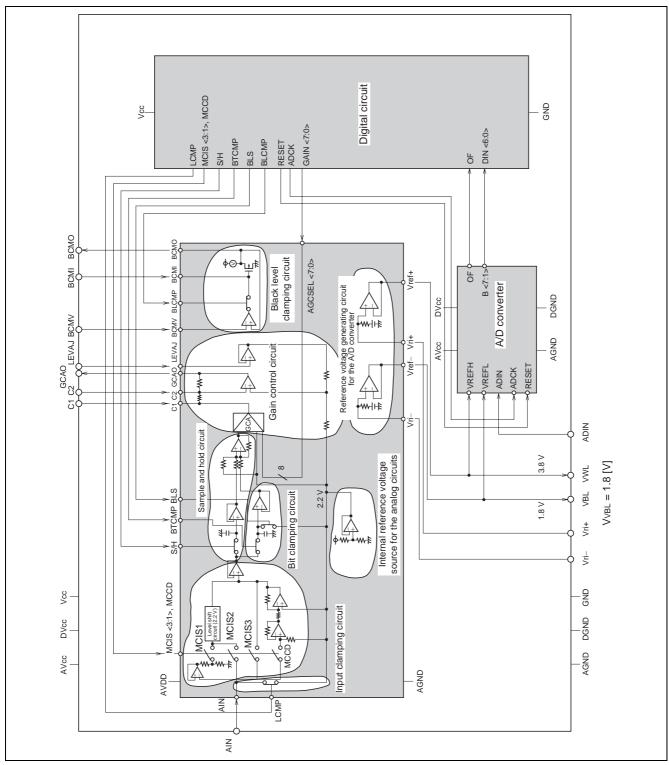

This controller contains not only the analog processing circuit, the A/D converter of a 7-bit flash type and image processing memory, but also the image sensor and the interface circuit to the CODEC (Coder and Decoder). Therefore, this LSI alone is capable of image processing.

#### **Features**

- High speed scan (Max 2 ms/line, Typ 5 ms/line)

- Compatibility with up to the B4 (8 pixels/mm, 16 pixels/mm) image sensor

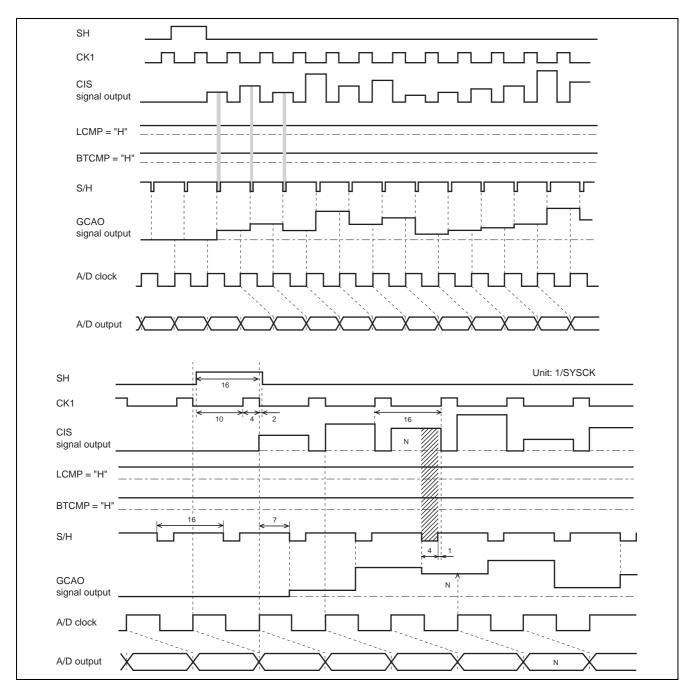

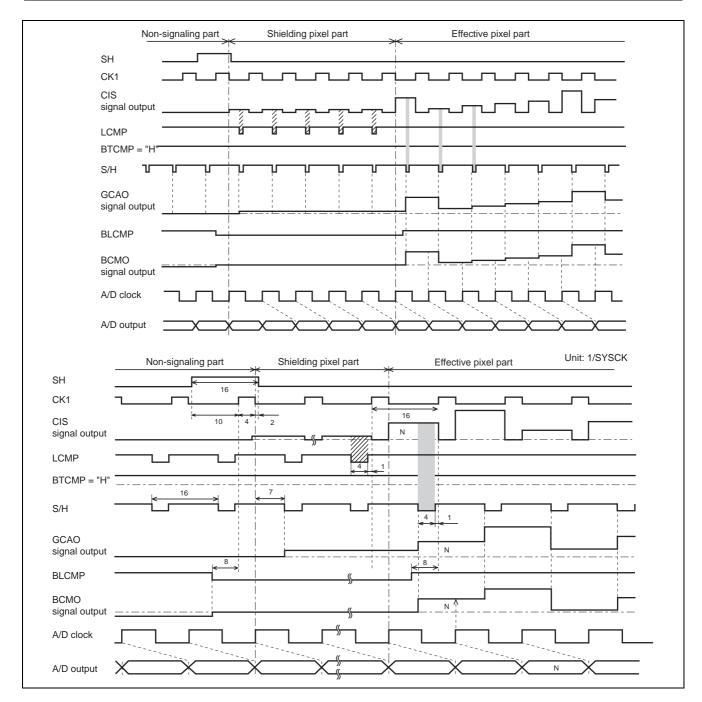

- Generation of control signals for the image sensor (CCD, CIS)

For CCD: SH, CK1, CK2, RS

For the contact sensor (CIS): SH, CK1, CK2

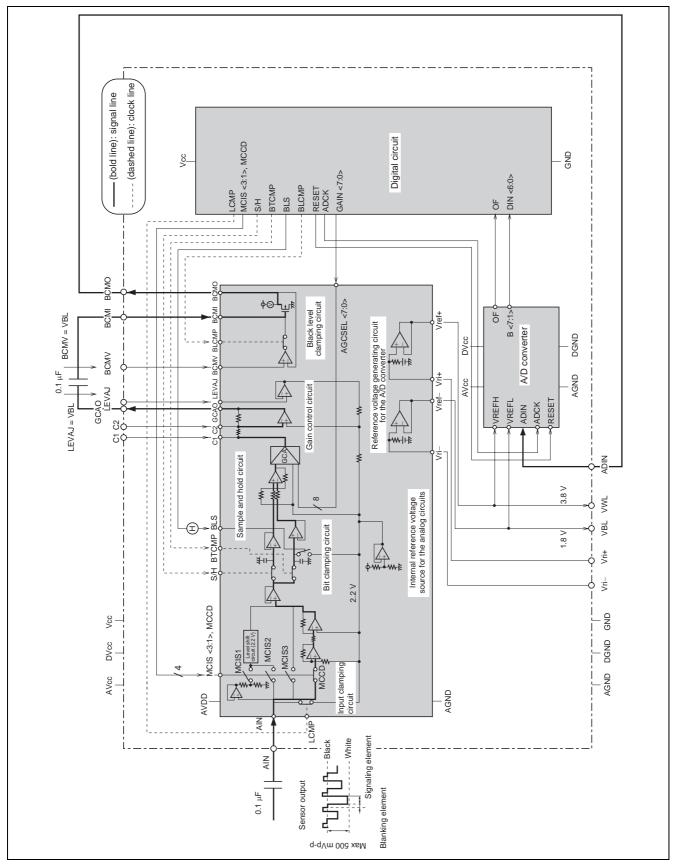

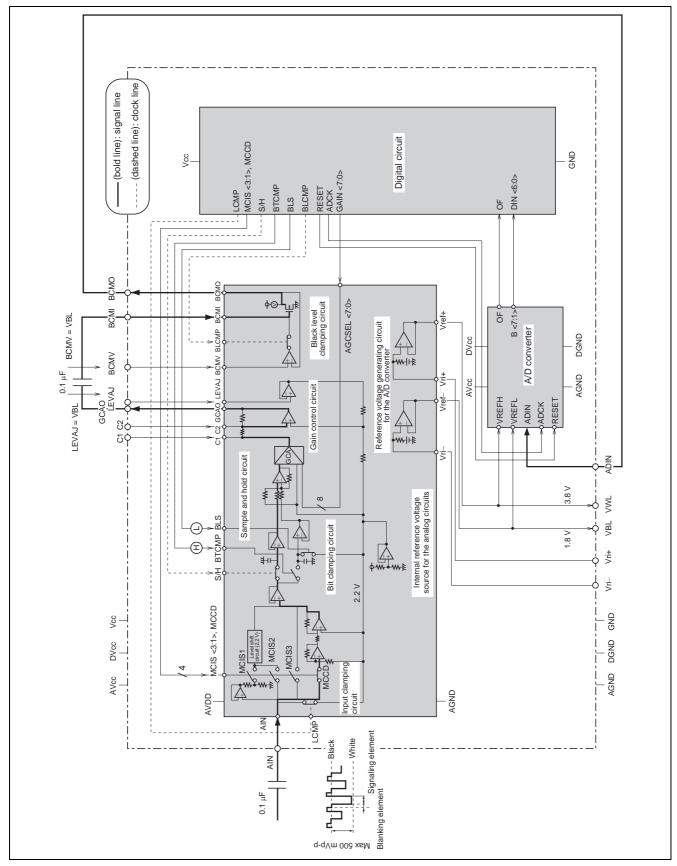

• Built-in analog processing circuit (equivalent to the M64291)

Sample and hold circuit

Gain control circuit

Black level clamping circuit

Reference internal power supply for the A/D converter

- Built-in A/D converter of a 7-bit flash type

- Built-in image processing memories

Uniformity correction memory, Line memory, Error memory, γ correction memory

• External output interface for converted binary data

Serial output ( $\rightarrow$  M66330)

DMA output

• External output interface for multivalued data

DMA transfer of data compensated for uniformity

• Various image processing functions

Uniformity correction

Resolution change from 50% to 200% (by the 1% step)

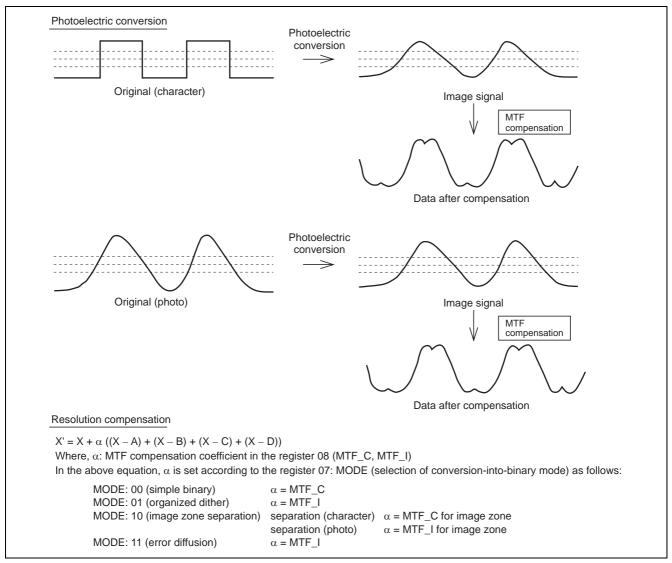

MTF compensation (2-dimensional processing, capable of correction for each character/photo)

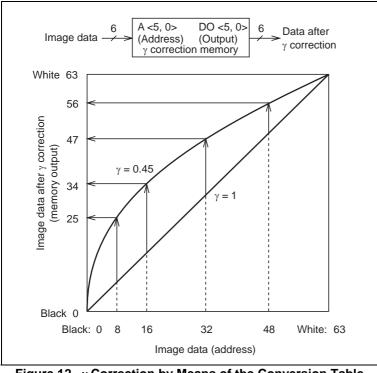

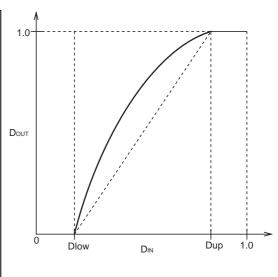

γ correction (capable of correction for each character/photo)

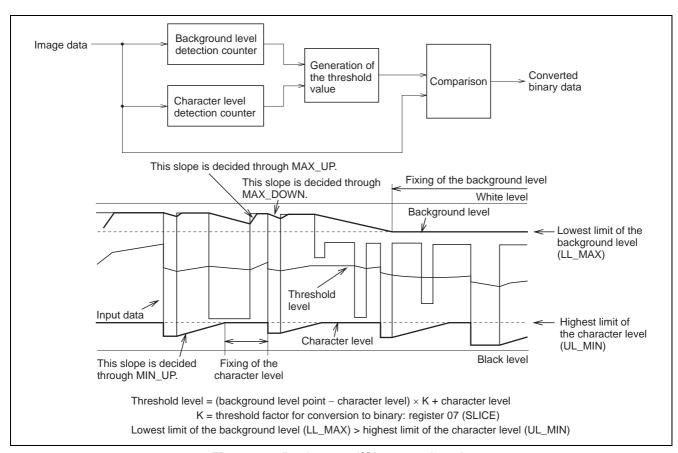

Detection of background/character levels

Change to pseudo-halftone

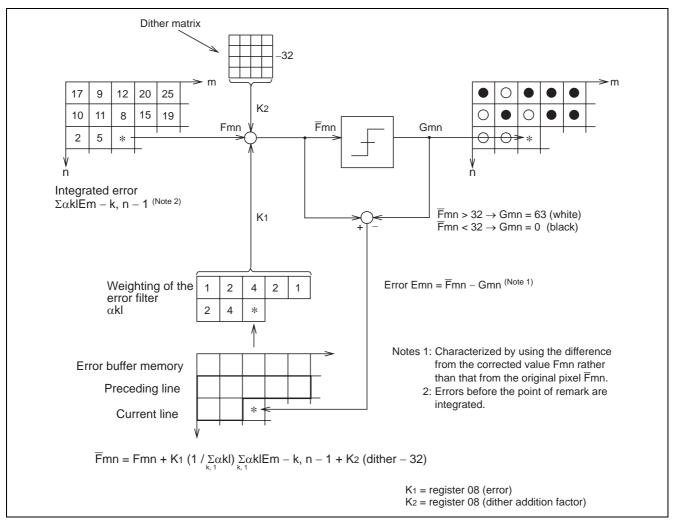

- Error diffusion (64 tone steps through 6-bit processing)

- Organized dither (64 tone steps through the  $8 \times 8$  matrix)

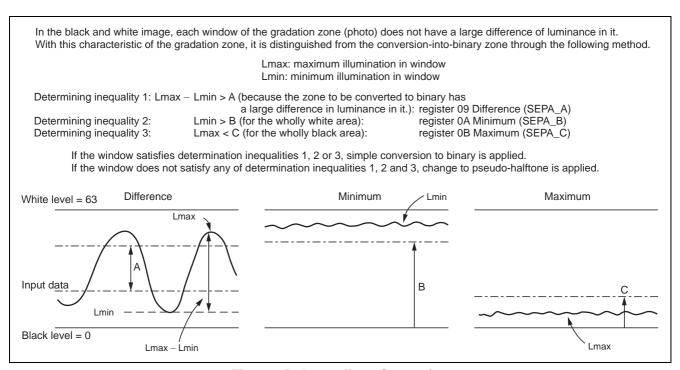

Image zone separation (2-dimensional processing)

• 5 V single power supply

### **Application**

Facsimile, word processor and image scanner

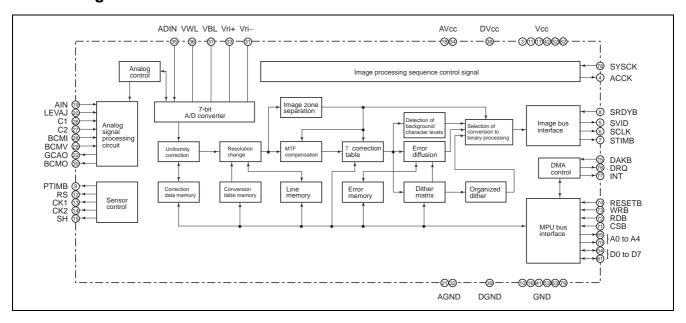

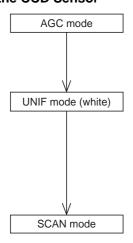

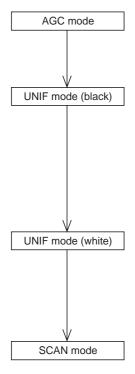

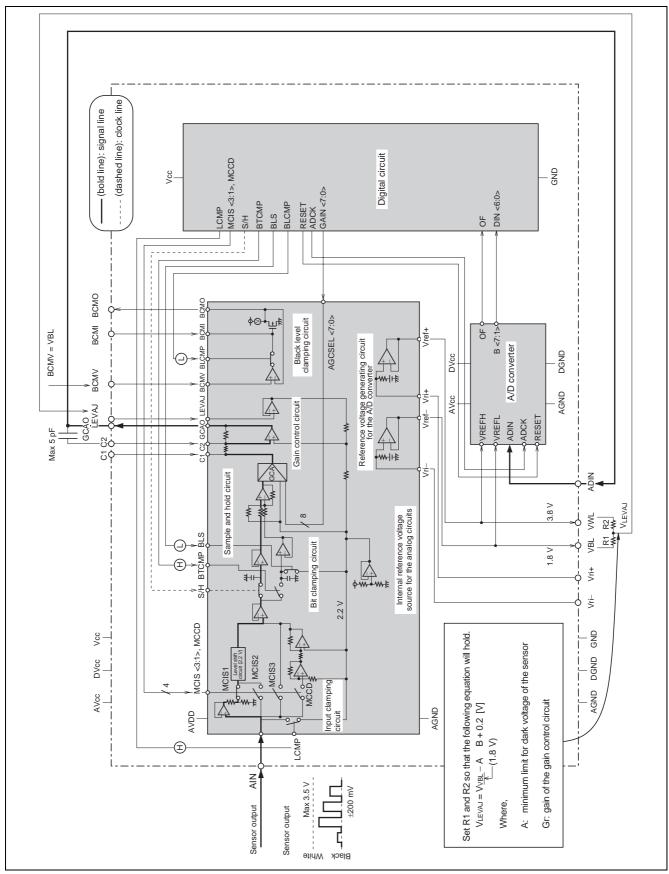

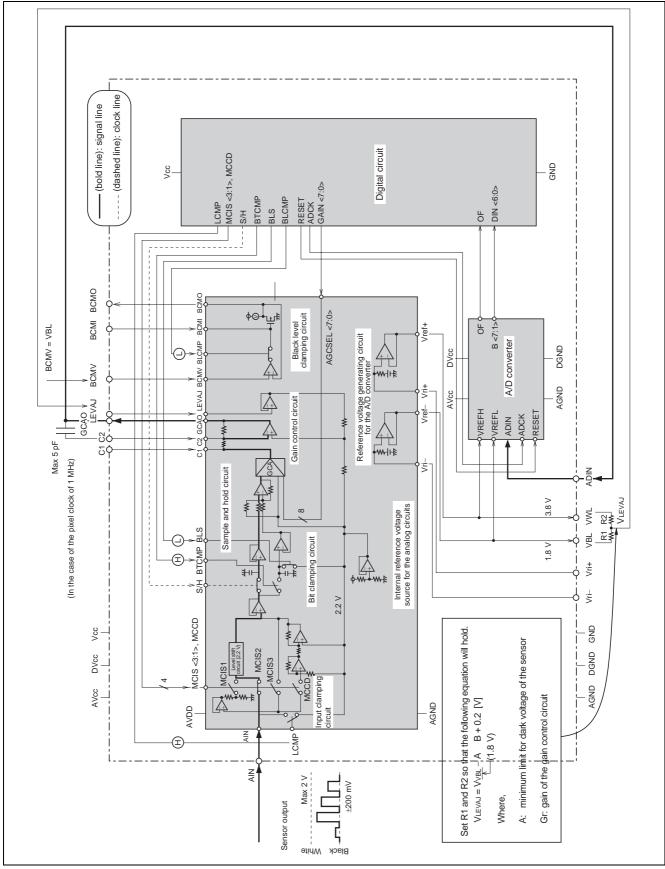

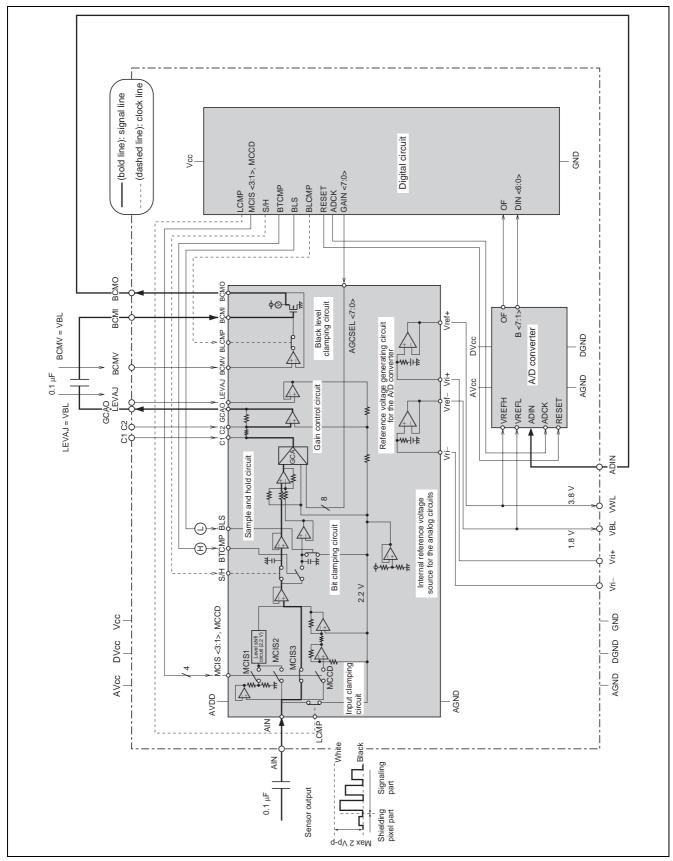

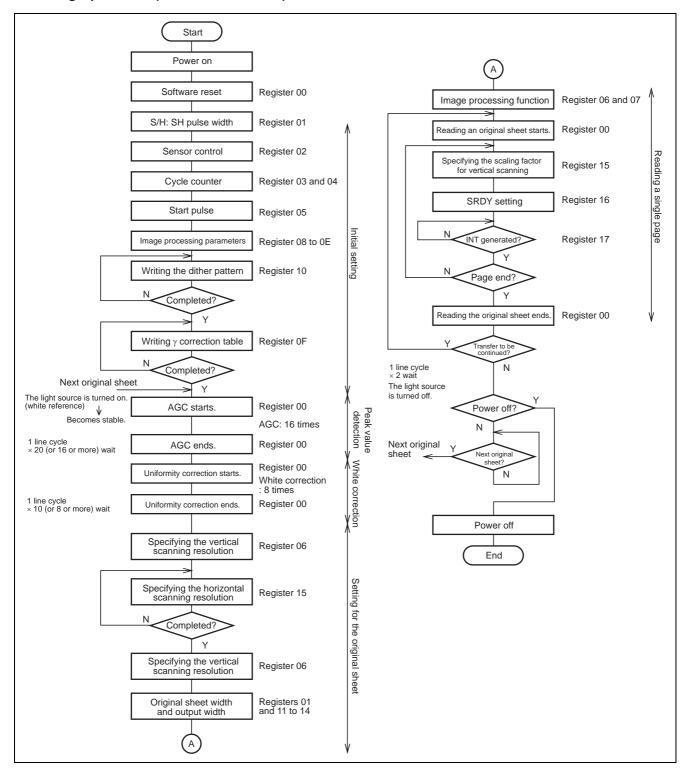

### **Block Diagram**

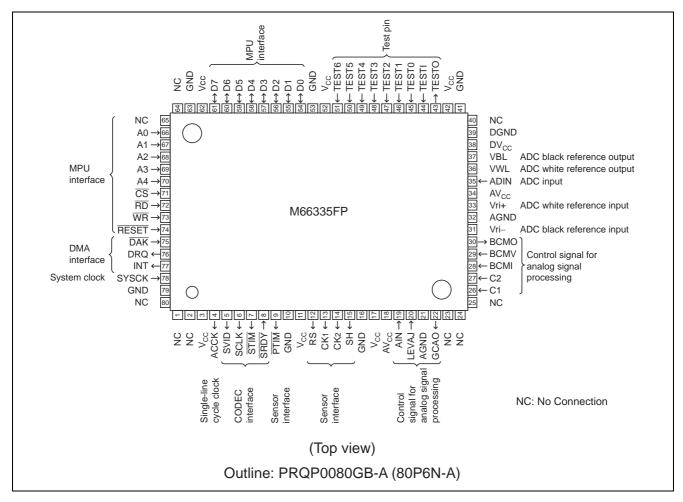

### **Pin Arrangement**

## Table 1 Image Processing Functions

| Image Processing Functions  | Specifications                                                                                                                        | Remarks                                                                                                                 |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Reading range               | • A4, B4                                                                                                                              |                                                                                                                         |

| Resolution                  | 8 pixels/mm, 16 pixels/mm (for the horizontal scanning direction)                                                                     |                                                                                                                         |

| Reading speed               | Typ: 5 ms/line; Max: 2 ms/line                                                                                                        | Controlled through the system clock                                                                                     |

| Uniformity correction       | <ul><li>White correction, black correction</li><li>Correction range: 50%</li></ul>                                                    | Correction memory is built-in     Readable from/writable in MPU                                                         |

| $\gamma$ correction         | Logarithmic correction                                                                                                                | <ul> <li>γ correction memory is built-in</li> <li>Capable of correction for each character/photo</li> </ul>             |

| MTF compensation            | Laplacian filter circuit through 2-<br>dimensional processing                                                                         | Correction memory is built-in     Capable of correction for each character/photo                                        |

| Simple conversion to binary | Floating slice system through the detection circuit for background/character levels                                                   |                                                                                                                         |

| Pseudo-halftone             | <ul> <li>Error diffusion: 6-bit processing (for 64 tone steps)</li> <li>Organized dither: 8 × 8 matrix (for 64 tone steps)</li> </ul> | Error buffer memory is built-in     64 W × 6 bits dither memory is built-in                                             |

| Image zone separation       | 2-dimensional processing through<br>luminance difference                                                                              |                                                                                                                         |

| Image reduction             | Range of the reduction rate: 50% to 100% (by the 1% step)                                                                             | Capable of outputting the average<br>line of a dropped line and the<br>subsequent line instead of both<br>lines         |

| Image enlargement           | Range of the enlargement rate: 100% to 200% (by the 1% step)                                                                          | Capable of outputting the average<br>line of a repeated line and the<br>subsequent line instead of the<br>repeated line |

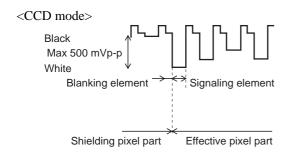

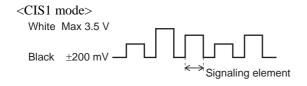

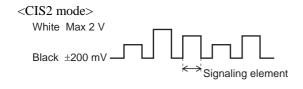

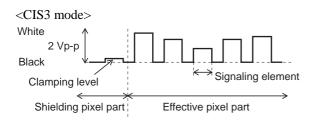

| Image sensor control signal | CIS image sensor (clock duty: 75%)     CCD image sensor                                                                               |                                                                                                                         |

| Analog processing           | The sample/hold circuit, gain control amplifier, black level clamping circuit, and 7-bit A/D converter are built-in.                  |                                                                                                                         |

## **Pin Description**

| the clock pulse signal for the shift register of the sensor reading circuit of CIS.  CK2 Output Reversed-phase pulses of CK1  RS Output Outputs the reset pulse to return the voltage at the floating capacitor of the CCD sensor to the initial one.  PTIM Output Outputs the pulse motor control signal for the reading roller.  CODEC SRDV Input Transfer start ready signal for data from CODEC interface  STIM Output Oelfines the data transfer section to CODEC SCLK Output Olopus image data in serial to CODEC SVID Output Outputs image data in serial to CODEC Output image data through the MPU bus OAM request signal to the external DMA controller to output in parallel image data through the MPU bus OAM request signal to the external DMA controller in response the above DROs signal Intr Output Single-line termination interrupt  Clock SYSCK Input System clock input pin Accord Coutput Input of the system reset. The cycle counter, register, F/F, and latch are reset.  MPU Input Control signal for MPU to access the M66335  RD Input Control signal for MPU to access the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M66335  RD Input Control signal for MPU to write data to the M663                                                                                                                                                                                                                                                                                              | Item       | Pin Name         | Input/Output | Function                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK1 Output Outputs the clock pubse signal to sequentially transfer out signaling electric charges from the sensor's transferring component for CCD and the clock pubse signal for the shift register of the sensor reading circuit CIS.  CK2 Output Reversed-phase pulses of CK1  RS Output Outputs the reset pulse to return the voltage at the floating capacitor of the CCD sensor to the initial one.  PTIM Output Outputs the pulse motor control signal for the reading roller.  CODEC SRDY Input Transfer start ready signal for data from CODEC interface  STIM Output Defines the data transfer section to CODEC SCLK Output Outputs image data in serial to CODEC SCLK Output Outputs image data in serial to CODEC SCLK Output Outputs image data in serial to CODEC DMA enders signal to transfer image data to CODEC DMA controller to output in parallel image data through the MPU bus DMA controller to output in parallel image data through the MPU bus DMA controller in response the above DRQ signal Intro Output Single-line termination interrupt  Clock SYSCK Input System clock input pin ACCK Output Single-line cycle clock  MPU interface  RESET Input Input Control signal for MPU to access the M66335  RESET Input Control signal for MPU to access the M66335  RESET Input Control signal for MPU to access the M66335  RESET Input Control signal for MPU to read data from the M66335  RESET Input Control signal for MPU to read data from the M66335  ROD Input Control signal for MPU to read data from the M66335  ROD Input Control signal for MPU to write data to the M66335  ROD POSITION OUTPUT Rest input pin. Hold this at "L".  TESTIO Output Test input pin. Hold this at "L".  TESTIO Output Test input pin. Hold this at "L".  TESTIO Output Test input pin. Hold this at "L".  TESTIO Output Test input pin. Hold this at "L".  TESTIO Output Positive power supply pin (rated supply voltage: 5 V)  DOND — Digital ground pin Input Positive power supply pin (rated supply voltage: 5 V)  POWER AVICE — Digital power supply pin (rated supply voltage: 5 V)  POWER AVICE                                                                                                                                                                                                                                                                                               |            | SH               | Output       | sensor's photoconductor component to its transferring component for                                                                                                                                                         |

| RS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | CK1              | Output       | Outputs the clock pulse signal to sequentially transfer out signaling electric charges from the sensor's transferring component for CCD and the clock pulse signal for the shift register of the sensor reading circuit for |

| the CCD sensor to the initial one.    PTIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | CK2              | Output       | Reversed-phase pulses of CK1                                                                                                                                                                                                |

| CODEC   Interface   SRDY   Input   Transfer start ready signal for data from CODEC   STIM   Output   Defines the data transfer section to CODEC   SVID   Output   Output   Clock signal to transfer image data to CODEC   SVID   Output   Outputs image data in serial to CODEC   SVID   Output   Outputs image data in serial to CODEC   SVID   Output   DMA request signal to the external DMA controller to output in parallel image data through the MPU bus   DMA controller in output in parallel image data through the MPU bus   DMA controller in response the above DRQ signal   INT   Output   Single-line termination interrupt   System clock input pin   ACCK   Output   Single-line cycle clock   MPU   RESET   Input   Single-line cycle clock   RESET   Input   Chip select signal for MPU to access the M66335   MRD   Input   Control signal for MPU to read data from the M66335   MRD   Input   Control signal for MPU to write data to the M66335   MRD   Input   Address signal to access various registers inside the M66335   MRD   Ot to D7   Input/Output   8-bit two way buffer   Positive power supply pin   GND   GND   GND pin   TESTI, 0 to 6   Input   Test input pin. Hold this at "L"   TESTI, 0 to 6   Input   Test output pin. Set this open.   Power   AVcc   — Analog power supply pin (rated supply voltage: 5 V)   DVcc   Digital power supply pin (rated supply voltage: 5 V)   DVcc   Digital power supply pin (rated supply voltage: 5 V)   DRND   DGND   Digital power supply pin (rated supply voltage: 5 V)   Input through capacity coupling and those from CIS, with no clamping levels, are input directly.)   LEVAJ   Input   Pin to control the Fequency characteristic of the gain control circuit.   The output voltage, V <sub>CcAO</sub> , is obtained by the following equation: V <sub>CCAO</sub> = V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> + G <sub>V</sub> × |            | RS               | Output       | Outputs the reset pulse to return the voltage at the floating capacitor of the CCD sensor to the initial one.                                                                                                               |

| interface   STIM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | PTIM             | Output       | Outputs the pulse motor control signal for the reading roller.                                                                                                                                                              |

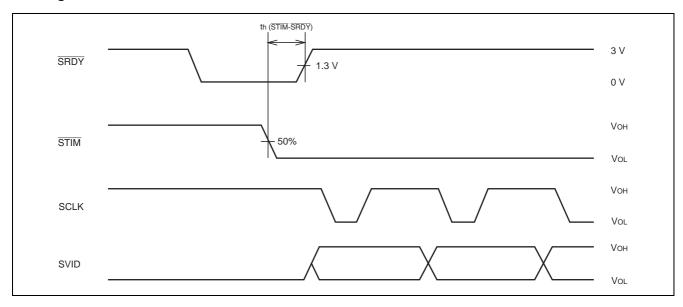

| SCLK   Output   Clock signal to transfer image data to CODEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CODEC      | SRDY             | Input        | Transfer start ready signal for data from CODEC                                                                                                                                                                             |

| SVID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | interface  | STIM             | Output       | Defines the data transfer section to CODEC                                                                                                                                                                                  |

| DMA interface   DRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | SCLK             | Output       | Clock signal to transfer image data to CODEC                                                                                                                                                                                |

| interface    DAK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | SVID             | Output       | Outputs image data in serial to CODEC                                                                                                                                                                                       |

| Test   Output   Single-line termination interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | DRQ              | Output       |                                                                                                                                                                                                                             |

| Clock         SYSCK         Input         System clock input pin           MPU interface         RESET         Input         Input of the system reset. The cycle counter, register, F/F, and latch are reset.           GS         Input         Chip select signal for MPU to access the M66335           RD         Input         Control signal for MPU to read data from the M66335           WR         Input         Address signal for MPU to write data to the M66335           A0 to A4         Input         Address signal to access various registers inside the M66335           Others         Vcc         —         Positive power supply pin           GND         —         GND pin           TESTI, 0 to 6         Input         Test input pin. Hold this at "L".           TESTO         Output         Test output pin. Set this open.           Power supply         AVcc         —         Analog power supply pin (rated supply voltage: 5 V)           GND         ACND         —         Analog ground pin           DVcc         —         Digital power supply pin (rated supply voltage: 5 V)           GND         —         Analog ground pin           DRND         —         Analog ground pin           DRND         —         Digital power supply pin (rated supply voltage: 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | DAK              | Input        | DMA acknowledge signal from the external DMA controller in response to the above DRQ signal                                                                                                                                 |

| ACCK Output Single-line cycle clock  MPU interface  RESET Input Input of the system reset. The cycle counter, register, F/F, and latch are reset.  CS Input Control signal for MPU to access the M66335  RD Input Control signal for MPU to read data from the M66335  WR Input Address signal to access various registers inside the M66335  A0 to A4 Input Address signal to access various registers inside the M66335  Others Vcc — Positive power supply pin  GND — GND pin  TESTI, 0 to 6 Input Test input pin. Hold this at "L".  TESTO Output Test output pin. Set this open.  Power AGND — Analog power supply pin (rated supply voltage: 5 V)  GND — Digital power supply pin (rated supply voltage: 5 V)  GND — Digital ground pin  DGND — Digital ground pin  DGND — Digital ground pin  DGND — Digital ground pin  Sensor signal control care input through capacity coupling and those from CIS, with no clamping levels, are input directly.)  Cain Control LEVAJ Input Pin to control the DC level of output signals of the gain control circuit. The output voltage, V <sub>GCAO</sub> , is obtained by the following equation:  V <sub>GCAO</sub> = V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where,  V <sub>LEVAJ</sub> voltage at LEVAJ V <sub>IN</sub> is the signal element corresponding to the signal level clamped through the input clamping circuit for CCD • CIS3 input or to the GND level for CIS1 • CIS2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | INT              | Output       | Single-line termination interrupt                                                                                                                                                                                           |

| MPU interface   RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Clock      | SYSCK            | Input        | System clock input pin                                                                                                                                                                                                      |

| MPU interface   RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | ACCK             | Output       |                                                                                                                                                                                                                             |

| CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | RESET            | <u> </u>     | Input of the system reset. The cycle counter, register, F/F, and latch are                                                                                                                                                  |

| RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | CS               | Input        | Chip select signal for MPU to access the M66335                                                                                                                                                                             |

| WR         Input         Control signal for MPU to write data to the M66335           A0 to A4         Input         Address signal to access various registers inside the M66335           D0 to D7         Input/Output         8-bit two way buffer           Others         Vcc         —         Positive power supply pin           GND         —         GND pin           TESTI, 0 to 6         Input         Test input pin. Hold this at "L".           TESTO         Output         Test output pin. Set this open.           Power supply         AVcc         —         Analog power supply pin (rated supply voltage: 5 V)           supply         DVcc         —         Digital power supply pin (rated supply voltage: 5 V)           GND         AGND         —         Analog ground pin           DGND         —         Digital ground pin           Sensor signal input part         Pin to input analog signals output from CCD or CIS (Signals from CCD are input through capacity coupling and those from CIS, with no clamping levels, are input directly.)           Gain control         C1, C2         Input         Pin to control the DC level of output signals of the gain control circuit. The output voltage, V <sub>GCAO</sub> , is obtained by the following equation: V <sub>GCAO</sub> = V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> coltage at LEVAJ V <sub>IN</sub> : input signal Gereal Capacity coupling in the signal level clamped through the input clamping circuit for CCD • CIS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | RD               | <u> </u>     |                                                                                                                                                                                                                             |

| A0 to A4 Input Address signal to access various registers inside the M66335    Do to D7   Input/Output   8-bit two way buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | WR               | Input        |                                                                                                                                                                                                                             |

| D0 to D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | A0 to A4         | <u> </u>     |                                                                                                                                                                                                                             |

| Others       V <sub>CC</sub> —       Positive power supply pin         GND       —       GND pin         TESTI, 0 to 6       Input       Test input pin. Hold this at "L".         TESTO       Output       Test output pin. Set this open.         Power supply       AV <sub>CC</sub> —       Analog power supply pin (rated supply voltage: 5 V)         GND       AGND       —       Digital power supply pin (rated supply voltage: 5 V)         GND       AGND       —       Analog ground pin         Sensor signal input part       Pin to input analog signals output from CCD or CIS (Signals from CCD are input through capacity coupling and those from CIS, with no clamping levels, are input directly.)         Gain control       C1, C2       Input       Pin to control the frequency characteristic of the gain control circuit         Circuit       LEVAJ       Input       Pin to control the DC level of output signals of the gain control circuit. The output voltage, V <sub>GCAO</sub> , is obtained by the following equation: V <sub>GCAO</sub> = V <sub>LEVAJ</sub> : voltage at LEVAJ V <sub>IN</sub> , where,         V <sub>LEVAJ</sub> : voltage at LEVAJ V <sub>IN</sub> is the signal element corresponding to the signal level clamped through the input clamping circuit for CCD • CIS3 input or to the GND level for CIS1 • CIS2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | D0 to D7         | Input/Output |                                                                                                                                                                                                                             |

| GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Others     | V <sub>CC</sub>  |              | Positive power supply pin                                                                                                                                                                                                   |

| TESTO Output Test output pin. Set this open.  Power supply DV <sub>CC</sub> — Analog power supply pin (rated supply voltage: 5 V)  BOND AGND — Digital power supply pin (rated supply voltage: 5 V)  Analog ground pin  DGND — Digital ground pin  Sensor signal input part  Gain control circuit  Circuit  Circuit  The output voltage, V <sub>GCAO</sub> , is obtained by the following equation:  V <sub>GCAO</sub> = V <sub>LEVAJ</sub> : voltage at LEVAJ  V <sub>IN</sub> : input signal Gv: gain of the gain control circuit  V <sub>IN</sub> is the signal element corresponding to the signal level clamped through the input clamping circuit for CCD • CIS3 input or to the GND level for CIS1 • CIS2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                  | _            | GND pin                                                                                                                                                                                                                     |

| TESTO Output Test output pin. Set this open.  Power supply DV <sub>CC</sub> — Analog power supply pin (rated supply voltage: 5 V)  BOND AGND — Digital power supply pin (rated supply voltage: 5 V)  Analog ground pin  DGND — Digital ground pin  Sensor signal input part  Gain control circuit  Circuit  Circuit  The output voltage, V <sub>GCAO</sub> , is obtained by the following equation:  V <sub>GCAO</sub> = V <sub>LEVAJ</sub> : voltage at LEVAJ  V <sub>IN</sub> : input signal Gv: gain of the gain control circuit  V <sub>IN</sub> is the signal element corresponding to the signal level clamped through the input clamping circuit for CCD • CIS3 input or to the GND level for CIS1 • CIS2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | TESTI, 0 to 6    | Input        | Test input pin. Hold this at "L".                                                                                                                                                                                           |

| Power supply       AV <sub>CC</sub> —       Analog power supply pin (rated supply voltage: 5 V)         GND       DV <sub>CC</sub> —       Digital power supply pin (rated supply voltage: 5 V)         GND       —       Analog ground pin         Sensor signal input part       AIN       Input       Pin to input analog signals output from CCD or CIS (Signals from CCD are input through capacity coupling and those from CIS, with no clamping levels, are input directly.)         Gain control control       C1, C2       Input       Pin to control the frequency characteristic of the gain control circuit.         Circuit       LEVAJ       Input       Pin to control the DC level of output signals of the gain control circuit.         Circuit       The output voltage, V <sub>GCAO</sub> , is obtained by the following equation: V <sub>GCAO</sub> = V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where,         V <sub>LEVAJ</sub> : voltage at LEVAJ       V <sub>IN</sub> : input signal         Gv: gain of the gain control circuit       V <sub>IN</sub> is the signal element corresponding to the signal level clamped through the input clamping circuit for CCD • CIS3 input or to the GND level for CIS1 • CIS2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | TESTO            | Output       | Test output pin. Set this open.                                                                                                                                                                                             |

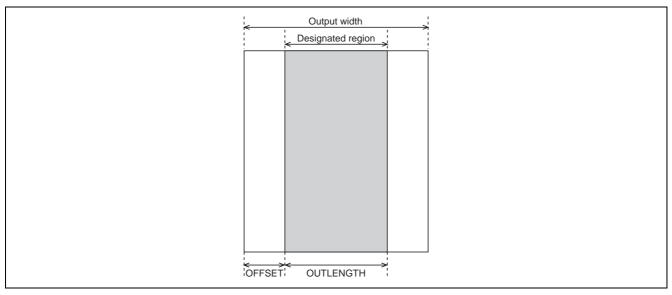

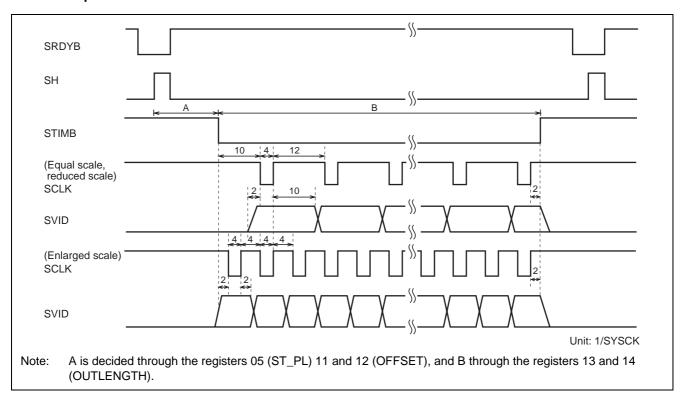

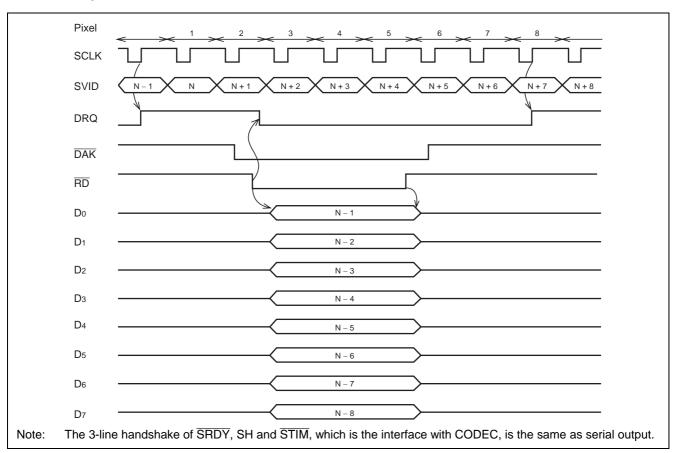

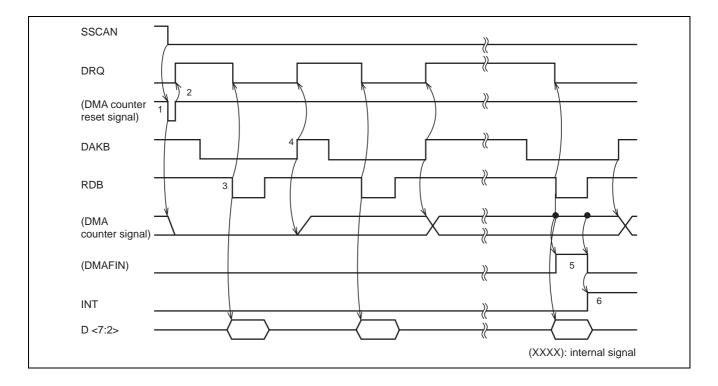

| supply       DV <sub>CC</sub> —       Digital power supply pin (rated supply voltage: 5 V)         GND       AGND       —       Analog ground pin         DGND       —       Digital ground pin         Sensor signal signal soutput from CCD or CIS (Signals from CCD are input through capacity coupling and those from CIS, with no clamping levels, are input directly.)         Gain control control       C1, C2       Input       Pin to control the frequency characteristic of the gain control circuit.         Circuit       LEVAJ       Input       Pin to control the DC level of output signals of the gain control circuit. The output voltage, V <sub>GCAO</sub> , is obtained by the following equation: V <sub>GCAO</sub> = V <sub>LEVAJ</sub> + G <sub>V</sub> × V <sub>IN</sub> , where, V <sub>LEVAJ</sub> : voltage at LEVAJ V <sub>IN</sub> : input signal G <sub>V</sub> : gain of the gain control circuit V <sub>IN</sub> is the signal element corresponding to the signal level clamped through the input clamping circuit for CCD • CIS3 input or to the GND level for CIS1 • CIS2 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power      | AV <sub>CC</sub> | <u> </u>     |                                                                                                                                                                                                                             |